Book contents

- Frontmatter

- Dedication

- Contents

- List of Contributors

- Preface

- 1 CMOS technology scaling and its implications

- 2 FinFETs: from devices to architectures

- 3 FDSOI technology and its implications for analog and digital design

- 4 Challenges and emerging trends of DSP-enabled frequency synthesizers

- 5 Digitally-assisted design of data converters

- 6 CMOS self-healing techniques for calibration and optimization of mm-wave transceivers

- 7 Analog-assisted digital design in mobile SoCs

- 8 Digitally-assisted RF design techniques

- 9 Digital controllers for switching power converters

- Appendix A

- Appendix B

- Index

- References

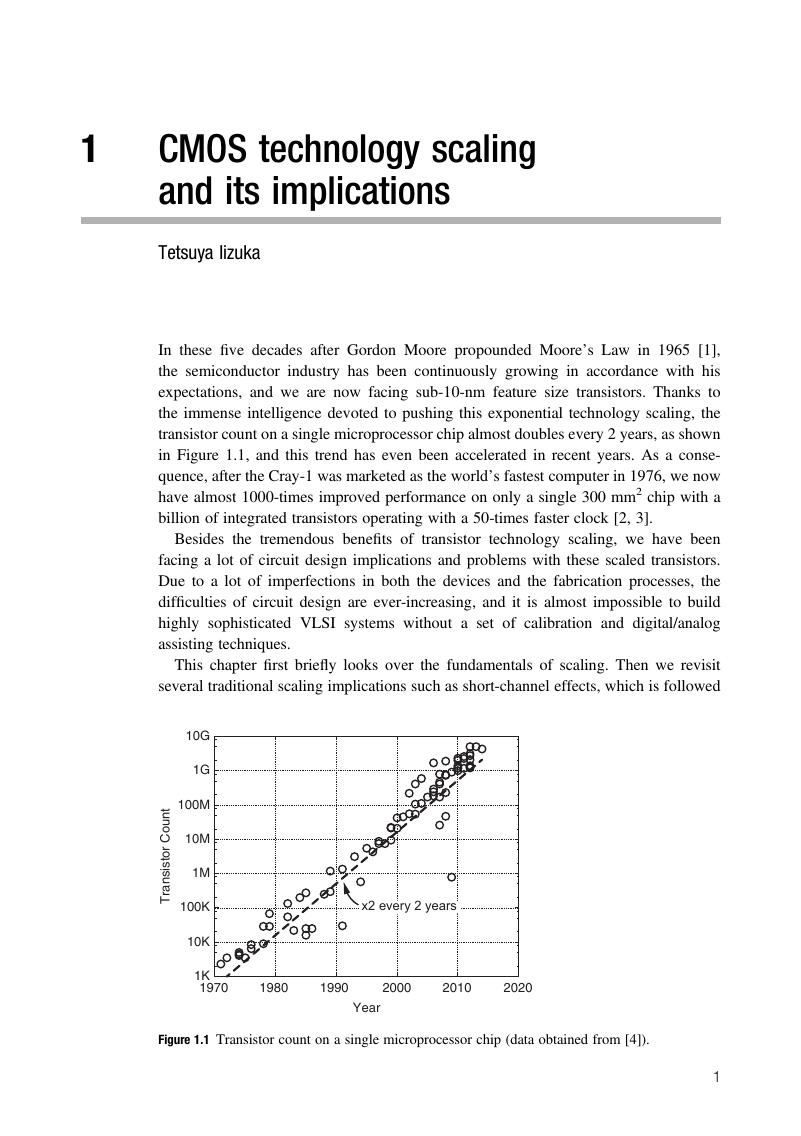

1 - CMOS technology scaling and its implications

Published online by Cambridge University Press: 05 August 2015

- Frontmatter

- Dedication

- Contents

- List of Contributors

- Preface

- 1 CMOS technology scaling and its implications

- 2 FinFETs: from devices to architectures

- 3 FDSOI technology and its implications for analog and digital design

- 4 Challenges and emerging trends of DSP-enabled frequency synthesizers

- 5 Digitally-assisted design of data converters

- 6 CMOS self-healing techniques for calibration and optimization of mm-wave transceivers

- 7 Analog-assisted digital design in mobile SoCs

- 8 Digitally-assisted RF design techniques

- 9 Digital controllers for switching power converters

- Appendix A

- Appendix B

- Index

- References

Summary

- Type

- Chapter

- Information

- Publisher: Cambridge University PressPrint publication year: 2015

References

- 5

- Cited by