Article contents

Three-dimensional hybrid bonding integration challenges and solutions toward multi-wafer stacking

Published online by Cambridge University Press: 07 October 2020

Abstract

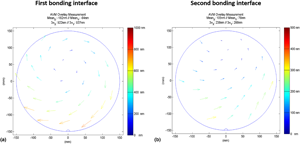

Recent applications require vertical chip stacking to increase the performance of many devices without the need of advanced node components. Image sensors and vision systems will embed more and more smart functions, for instance, image processing, object recognition, and movement detection. In this perspective, the combination of Cu-to-Cu direct hybrid bonding technology with Through-Silicon-Via (TSV) will allow 3D interconnection between pixels and the associated computing and memory structures, each function fabricated on a separate wafer. Wafer-to-wafer hybrid bonding was achieved with multi-pitch design—1–4 μm—of single levels of Cu damascene patterned on 300 mm silicon substrates. Defect-free bonding, as far as the extreme edge of the wafer, was demonstrated on a stack with three wafers. Middle wafers thinning was done with grinding only and with a thickness uniformity (TTV) <2 μm to an ultimate thinning as low as 3 μm. Alignment performance was characterized by post-bonding for two superposed hybrid bonding interfaces. In our set of wafers, modeling the alignment with translation, rotation, and scaling components enables us to optimize the residuals down to 3σ < 100 nm. A process flow of thin TSV with a fine pitch of 2 μm for high-density vertical interconnect through a three-wafer stack was developed. Via-last TSV architecture was adopted with 1 μm TSV diameter and 10 μm thickness. Lithography, etching solutions, Ti/TiN barrier deposition, and void-free Cu filling solutions were demonstrated. TSV cross sections after CMP and connections with top and bottom Cu damascene lines show good profile control. Process developments are matured and can be reliably used in the fabrication of an electrical test vehicle including vertical interconnects associating multi-wafers stacking with a hybrid bonding process and high-density thin TSV applicable to low pitches (<5 μm).

- Type

- Prospective Articles

- Information

- Copyright

- Copyright © The Author(s), 2020, published on behalf of Materials Research Society by Cambridge University Press

References

- 12

- Cited by