Article contents

Neuromorphic-based Boolean and reversible logic circuits from organic electrochemical transistors

Published online by Cambridge University Press: 10 August 2020

Abstract

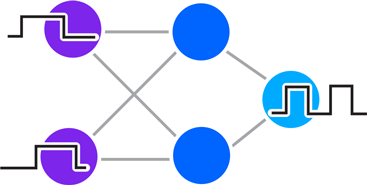

We show the design and simulation of organic neuromorphic circuits in a hybrid-computation approach that emulates Boolean and reversible logic gates based on multigate organic electrochemical transistors (OECTs). The organic neuromorphic circuits consist of input, hidden, and output layers that can carry out Boolean operations, including the Exclusive OR (XOR) function, with five or less OECTs. The multigate functionality of OECTs is harnessed to perform the summation function of the neurons. Connection weights of the networks are defined in an unconventional way that depends on the value of the drain-source current of the outputting neuron, which changes according to the input values of the circuit. The Boolean circuits can be cascaded together to build higher level circuits and are demonstrated to form a full adder circuit and the Double Feynman and Toffoli reversible logic gates. Using realistic experimental parameters, the energy per computation is estimated to be ~2.3 nJ for circuit designs with a bias voltage of 0.5 V, with ~230 fJ or less being achievable for lower bias voltages.

- Type

- Organic Semiconductors for Brain-Inspired Computing

- Information

- MRS Bulletin , Volume 45 , Issue 8: Organic Semiconductors for Brain-Inspired Computing , August 2020 , pp. 649 - 654

- Copyright

- Copyright © Materials Research Society 2020

References

- 6

- Cited by