## Electrical Probing and Current Imaging for Failure Analysis in the SEM/FIB.

Stephan Kleindiek<sup>1</sup>, Andreas Rummel<sup>1</sup>, Klaus Schock<sup>1</sup>, Gregor Renka<sup>1</sup>, Matthias Kemmler<sup>1</sup>

<sup>1</sup>Kleindiek Nanotechnik, Reutlingen, Germany

As the transistors and other circuits in semiconductor devices shrink to smaller and smaller sizes, failure analysis on these devices is becoming more and more challenging. There is a large need for highly precise nano-probers to quickly and reliably address contacts in the range of few tens of nanometers. Using piezo-driven micromanipulators, individual nano-scale components on semiconductor devices can be tested inside a SEM or FIB system.

The SEM is primarily used for imaging the nano-scale contacts. Due to the multi-layer nature of modern semiconductor products, the FIB is used to reveal the layer of interest, deposit conductive, resistive, or insulating patches for modification of the circuit, as well as clean the sample to remove contamination or oxide layers in order to gain access to the structure of interest. A SEM/FIB system is also important for shaping (and re-shaping) as well as cleaning the probe tips, which are used to contact the nano-scale structures of interest.

Next to actually contacting the sample, various tools are necessary to successfully characterize the structure of interest efficiently. Safely landing tips – without bending them – as well as ensuring that they are in low-ohmic contact with the substrate is important for reliable measurements.

Further, methods such as EBIC and EBAC can be used to gather information on buried structures; this facilitates locating the area of interest.

Finally, Current Imaging, a method for imaging the sample's current response to a biased needle that is swept over its surface, is described.

In this work, we demonstrate the successful characterization of state of the art 22 nm transistors using the methods described above.

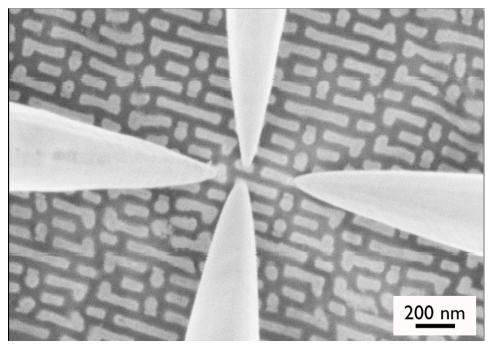

**Figure 1.** Four probes in contact with two transistors.

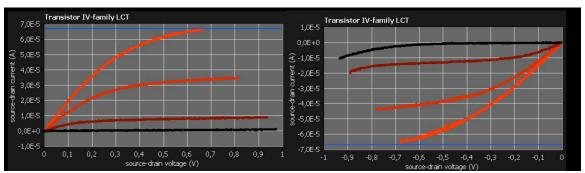

**Figure 2.** Acquired curves from above transistors. Both transistors share the same gate (9 o'clock tip) as well as the same drain (6 o'clock tip). The n-MOS source is contacted by the tip at 3 o'clock, the p-MOS source by the tip at 12 o'clock.