## Novel FIB-less Fabrication of Electrical Devices for in-situ Biasing

Rohan Dhall<sup>1</sup>, Houston Dycus<sup>1</sup>, Matthew Cabral<sup>1</sup>, Everett Grimley<sup>1</sup>, Weizong Xu<sup>1</sup>, John Damiano<sup>2</sup>, and James M. LeBeau<sup>1</sup>

In this study, we report a novel fabrication scheme for *in-situ* electrical biasing of bulk material systems. This scheme integrates simple microelectronics fabrication processes with conventional TEM sample preparation through mechanical polishing, to produce electrical devices suitable for high resolution TEM/STEM studies under applied electrical bias. This is particularly crucial for applications such as quantitative STEM imaging, where FIB-induced sample damage distorts the image contrast, and prevents precise quantification.

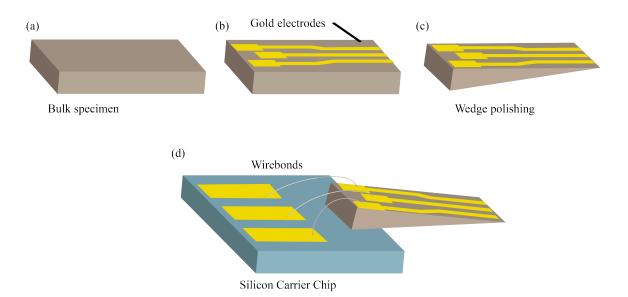

We begin sample fabrication with the mechanical polishing of bulk specimens, which can be either single crystal, or polycrystalline material. The purpose of this step is to produce a smooth surface for subsequent fabrication steps. After this, we coat the specimens with a photoresist, and expose them to UV radiation through a photomask. Then, we develop the photoresist in a solvent, and deposit a film of metal contacts (typically, a bilayer of Chrome and Gold, typically 300nm thick), using an electron beam metal evaporator in high vacuum. This is followed by a liftoff process, which removes the photoresist from the substrate, and leaves behind metal contacts to the bulk wafer. The typical spacing between metal contacts can be as small as 300nm using advanced photoaligners and steppers. However, for this study, we use electrodes separated by 10-20 microns.

We then wedge polish the sample to electron transparency using an Allied Multiprep tool on the side of wafer where no metal electrodes are deposited, as described elsewhere[1]. Then, the thin TEM sample is attached to a home-fabricated silicon carrier chip, with pre-patterned metal electrodes. Finally, we connect desired electrodes on the wedge polished sample to the metal pads on the silicon carrier chip using wirebonding. This allows us to apply electrical voltages to the electron transparent region of the wedge polished TEM sample.

This fabrication scheme offers several advantages over other methods, which rely on FIB lift outs. In particular, the issue of FIB damage does not affect our measurements. Also, it is possible to obtain regions as thin as a few tens of nanometers, ideal for high resolution STEM imaging. Using the Protochips Fusion double tilt holder, we are also able to tilt single crystal samples onto zone-axis, enabling atomic resolution STEM imaging and spectroscopy. We will discuss the application of this technique to study lattice distortions in ferroelectric materials such as lead titanate and lead zirconium titanate, under externally applied electric fields (see Figure 2).

## References:

[1] Voyles, P. M. J. L. Grazul, and D. A. Muller, "Imaging individual atoms inside crystals with ADF-STEM." *Ultramicroscopy* **96**.3 (2003): p251-273.

<sup>&</sup>lt;sup>1.</sup> Department of Material Science and Engineering, North Carolina State University, Raleigh, NC, USA

<sup>&</sup>lt;sup>2</sup> Protochips Inc., Morrisville, NC, USA

**Figure 1.** A schematic representation of the fabrication scheme used for in-situ sample preparation. (a) shows a bulk sample, on which electrodes are deposited using photolithography (b). Following this, the sample is thinned by mechanical wedge polishing, as shown in (c). Finally, the sample is attached to a silicon carrier chip, wirebonded, and loaded into the microscope.