## Nano Focus

**Electron clouds distortion** on graphene surface harm conductivity

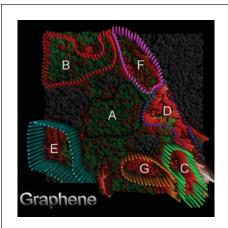

**▼** raphene, which comprises a single layer of carbon atoms linked in a honeycomb-like arrangement, is highly conductive. However, a research team has produced a series of images that reveal how folds and ripples in this material can limit its conductivity. Under ideal circumstances, when graphene is completely flat, electric charges speed through it without encountering many obstacles, said Sarbajit Banerjee of the State University of New York, Buffalo, one of the researchers who published the study in the June 28 online edition of Nature Communications (DOI: 10.1038/ ncomms1376). However conditions are not always optimal.

The images demonstrate that when graphene is folded or bent, the electron cloud lining its surface also becomes distorted. This makes it more difficult for an electric charge to travel through.

Banerjee, D.A. Fischer of the National Institute of Standards and Technology, P.S. Lysaght of SEMATECH, D. Prendergast of the Lawrence Berkeley National Laboratory, and their colleagues used scanning transmission x-ray microscopy and near edge x-ray absorption fine structure (NEXAFS) to create the images, and the experiments were further supported by computer simulations.

"Using simulations, we can better understand the measurements our colleagues made using x-rays, and better predict how subtle changes in the structure of graphene affect its electronic properties," said Prendergast. "We saw that regions of graphene sloped at different angles, like looking down onto the slanted roofs of many houses packed close together."

Besides documenting how folds in graphene distort its electron cloud, the research team also discovered that contaminants that cling to graphene during processing linger in valleys created in the material where it is uneven. Such contaminants uniquely distort the electron cloud, thereby changing the strength with which the cloud is bound to the underlying atoms.

"It's not well understood how to transfer graphene onto substrata without

Imaging electronic domains in graphene: Dotted lines show distinctive regions of graphene that are sloped at different angles. Soft x-rays paint a bird's-eye view of the electron cloud of graphene. The image is 4  $\mu$ m × 4  $\mu$ m. *Photo Credit*: Brian J. Schultz.

it folding onto itself," Banerjee said. The study suggests that companies hoping to incorporate graphene into products such as conductive inks, ultrafast transistors, and solar panels could benefit from more basic research on the nanomaterial. Improved processes for transferring flat sheets of graphene onto commercial products could greatly increase the efficiency of those materials.

**Atomically smooth** polycrystalline silicon waveguides fabricated

tomically smooth optical fibers Amade of polycrystalline silicon are advancing microscale optoelectronics. In the July 1 issue of Optics Letters (DOI:10.1364/OL.36.002480; p. 2480), N. Healy of the University of Southampton, F.R. Sparks of Pennsylvania State University, and their colleagues detail their process for creating optical waveguides with an unprecedentedly low level of surface scattering.

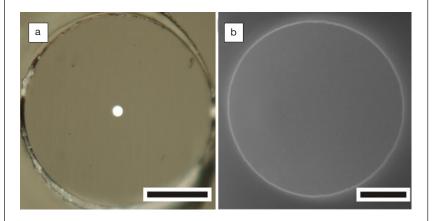

The research team used 500°C silane and helium gas to deposit silicon in the pores of 5.6 µm and 1.3 µm internal diameter silica capillaries before annealing the constructs at 1325°C. The resulting waveguides possessed a

(a) Optical microscope image of the 5.6 µm polysilicon core fiber as prepared for optical coupling, scale bar 50 µm. (b) Helium ion microscope image of the 1.3 µm core, scale bar 400 nm. Reproduced with permission from Opt. Lett. 36(13)v(2011), DOI:10.1364/OL.36.002480; p. 2480. © 2011 Optical Society of America.

surface roughness of  $\sigma = 0.1$  nm RMS with z-direction resolution of 0.01 nm RMS. This surface roughness is an order of magnitude less than what has been

previously measured in polycrystalline waveguides, and is also lower than that of a competing fabrication process, etchless silicon-on-insulator. The high